DS90CR218A

DS90CR218A is +3.3V Rising Edge Data Strobe LVDS manufactured by Texas Instruments.

.ti.

SNLS054D

- NOVEMBER 1999

- REVISED APRIL 2013

DS90CR218A +3.3V Rising Edge Data Strobe LVDS 21-Bit Channel Link

- 12 MHz to 85 MHz

Check for Samples: DS90CR218A

Features

- 12 to 85 MHz Shift Clock Support

- 50% Duty Cycle on Receiver Output Clock

- Low Power Consumption

- ±1V mon-mode Range (Around +1.2V)

- Narrow Bus Reduces Cable Size and Cost

- Up to 1.785 Gbps Throughput

- Up to 223 Mbytes/sec Bandwidth

- 345 m V (typ) Swing LVDS Devices for Low EMI

- PLL Requires No External ponents

- Rising Edge Data Strobe

- patible with TIA/EIA-644 LVDS Standard

- Low Profile 48-Lead TSSOP Package

DESCRIPTION

The DS90CR218A receiver deserializes three input LVDS data streams into 21 bits of CMOS/TTL output data. When operating at the maximum input clock rate of 85 Mhz, the LVDS data is received at 595 Mbps per data channel for a total data throughput of 1.785 Gbit/sec (233 Mbytes/sec).

The narrow bus and LVDS signalling of the DS90CR218A is an ideal means to solve EMI and cable size problems associated with wide, high-speed TTL interfaces.

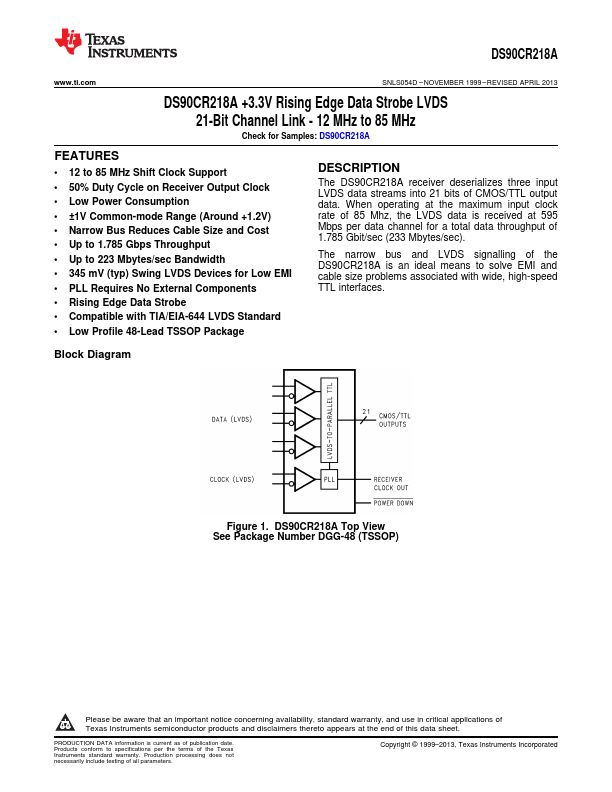

Block Diagram

Figure 1. DS90CR218A Top View See Package Number DGG-48 (TSSOP)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999- 2013, Texas Instruments Incorporated

SNLS054D

- NOVEMBER...